Low-energy DSP IP optimizes power, performance and area, offering up to 40% area savings for mobile, automotive, consumer and hyperscale computing markets

SAN JOSE, Calif. — (BUSINESS WIRE) — June 17, 2021 — Cadence Design Systems, Inc. (Nasdaq: CDNS) today unveiled the Cadence® Tensilica® FloatingPoint DSP family, which provides a scalable and configurable solution designed specifically for floating-point-centric workloads. Optimized for power, performance and area (PPA), the new DSP IP cores extend from small, ultra-low power to very high performance and are well-suited for a broad array of applications. These range from energy-efficient solutions for battery-operated devices to artificial intelligence/machine learning (AI/ML), motor control, sensor fusion, object tracking and augmented reality/virtual reality (AR/VR) applications in the mobile, automotive, hyperscale computing and consumer markets.

This press release features multimedia. View the full release here: https://www.businesswire.com/news/home/20210617005326/en/

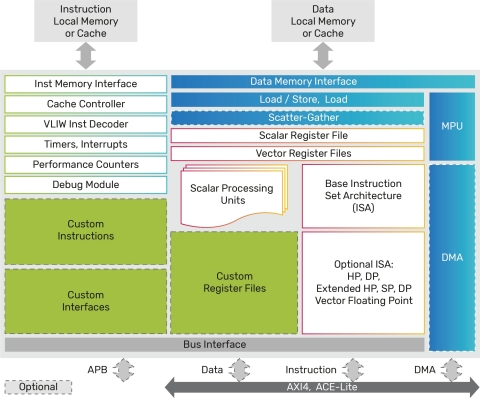

The highly scalable Cadence® Tensilica® FloatingPoint DSP family offers system-on-chip designers peace of mind when designing a solution that meets their power, performance and area budget. When much higher performance and clock speed are required, the FloatingPoint KQ7 and KQ8 DSPs provide greater throughput. (Graphic: Business Wire)

The new family is comprised of four cores: the Tensilica FloatingPoint KP1 DSP, the Tensilica FloatingPoint KP6 DSP, the Tensilica FloatingPoint KQ7 DSP and the Tensilica FloatingPoint KQ8 DSP. Early customer feedback has been overwhelmingly positive, with evaluations demonstrating significant benefits in PPA. For more information on the new DSPs, please visit www.cadence.com/go/tensilicafloatingpoint.

“Floating-point numbers, common in technical computations, underpin a host of radar applications that process large or unpredictable data sets. We’ve successfully collaborated with Cadence on multiple generations of IP cores and are pleased to see them addressing this critical market need and expanding their proven Tensilica product line,” said Ian Podkamien, VP and Head of Automotive at Vayyar Imaging. “FloatingPoint DSPs optimized for a variety of applications can enable Vayyar’s system-on-chip sensors to improve energy efficiency and performance across the automotive, elder care, smart home, retail, HLS, robotics and medical industries, among others.”

Tensilica FloatingPoint DSPs share a common instruction set architecture (ISA) with existing Tensilica DSPs’ optional vector floating-point unit (VFPU), promoting software portability and reusability while enabling easy offloading of floating-point workloads. Scalable from 128-bit SIMD to 1024-bit SIMD on both the Tensilica Xtensa® LX and NX platforms, the new FloatingPoint DSPs deliver a 25% improvement in fused multiply-add (FMA) operations compared to Tensilica fixed-point DSPs with the VFPU add-on, contributing to greater operational throughput. Performance can be further enhanced and differentiated using the Tensilica Instruction Extension (TIE) language. In addition, the FloatingPoint DSPs offer up to 40% area savings compared to the similar class of fixed-point DSPs with VFPUs.

High-performance software tools accompanying the new DSPs provide effective auto-vectorization that helps optimize the scalar code to utilize the vector floating-point units with minimal to no manual effort. Support for optimized Eigen, NatureDSP, simultaneous location and mapping (SLAM) and math software libraries enables easier development of high-performance software. The Tensilica FloatingPoint DSPs offer a software development environment that enables seamless migration of the existing floating-point common software stack to the new Tensilica FloatingPoint DSPs and between the FloatingPoint DSPs within the family.

“Floating-point numbers are used widely in modern computations across a broad range of compute-intensive applications, and the need for floating-point processing is growing,” said Larry Przywara, senior group director, Tensilica marketing at Cadence. “Energy-efficient, cost-effective and high-performance DSPs designed specifically for floating-point-centric computation are critical for developing competitive and differentiated products. The scalable Tensilica FloatingPoint DSP family provides optimal PPA for these floating-point computations, regardless of the application. These DSPs are an example of how Cadence is applying our computational software prowess to hardware to solve our customers’ design challenges.”

The Tensilica FloatingPoint DSPs support Cadence’s Intelligent System Design™ strategy by enabling SoC design excellence. The Tensilica FloatingPoint KP1 DSP, Tensilica FloatingPoint KP6 DSP, Tensilica FloatingPoint KQ7 DSP and Tensilica FloatingPoint KQ8 DSP are all in general availability now.

About Cadence

Cadence is a pivotal leader in electronic design, building upon more than 30 years of computational software expertise. The company applies its underlying Intelligent System Design strategy to deliver software, hardware and IP that turn design concepts into reality. Cadence customers are the world’s most innovative companies, delivering extraordinary electronic products from chips to boards to systems for the most dynamic market applications, including consumer, hyperscale computing, 5G communications, automotive, mobile, aerospace, industrial and healthcare. For seven years in a row, Fortune magazine has named Cadence one of the 100 Best Companies to Work For. Learn more at cadence.com.

© 2021 Cadence Design Systems, Inc. All rights reserved worldwide. Cadence, the Cadence logo and the other Cadence marks found at www.cadence.com/go/trademarks are trademarks or registered trademarks of Cadence Design Systems, Inc. All other trademarks are the property of their respective owners.

View source version on businesswire.com: https://www.businesswire.com/news/home/20210617005326/en/

Contact:

For more information, please contact:

Cadence Newsroom

408-944-7039

newsroom@cadence.com