DNA 100 processor easily scales from 0.5 to 100s of TMACs for neural network inferencing in automotive, surveillance, robotics, drones, AR/VR, smartphone, smart home and IoT products

SAN JOSE, Calif. — (BUSINESS WIRE) — September 19, 2018 — Cadence Design Systems, Inc. (NASDAQ: CDNS) today announced the Cadence® Tensilica® DNA 100 Processor IP, the first deep neural-network accelerator (DNA) AI processor IP to deliver both high performance and power efficiency across a full range of compute from 0.5 TeraMAC (TMAC) to 100s of TMACs. As a result, the DNA 100 processor is well suited for on-device neural network inference applications spanning autonomous vehicles (AVs), ADAS, surveillance, robotics, drones, augmented reality (AR)/virtual reality (VR), smartphones, smart home and IoT. The DNA 100 processor delivers up to 4.7X better performance and up to 2.3X more performance per watt compared to other solutions with similar multiplier-accumulator (MAC) array sizes. For more information, visit www.cadence.com/go/dna100.

This press release features multimedia. View the full release here: https://www.businesswire.com/news/home/20180919005053/en/

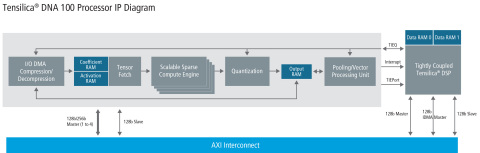

The Cadence Tensilica® DNA 100 Processor IP features specialized hardware blocks that enable up to 4.7X better performance and up to 2.3X more performance per watt compared to other solutions with similar MAC array sizes. (Graphic: Business Wire)

Neural networks are characterized by inherent sparsity for both weights and activations, causing MACs in other processors to be consumed unnecessarily through loading and multiplying zeros. The DNA 100 processor’s specialized hardware compute engine eliminates both tasks, allowing this sparsity to be leveraged for power efficiency and compute reduction. Retraining of neural networks helps increase the sparsity in the networks and achieve maximum performance from the DNA 100 processor’s sparse compute engine. This enables the DNA 100 processor to maximize throughput with a smaller array, as evidenced by its ability to achieve up to 2,550 frames per second (fps) and up to 3.4TMACs/W (in 16 nm) of estimated on-device inference performance on ResNet 50 for a 4K MAC configuration.

“The applications for AI processors are growing rapidly, but running the latest neural network models can strain available power budgets,” said Mike Demler, senior analyst at the Linley Group. “Meeting the demands for AI capabilities in devices ranging from small, battery-operated IoT sensors to self-driving cars will require more efficient architectures. The innovative sparse compute engine in Cadence’s new Tensilica DNA 100 processor addresses these limitations and packs a lot of performance for any power budget.”

The DNA 100 processor comes equipped with a complete AI software platform. Compatibility with the latest version of the Tensilica Neural Network Compiler enables support for advanced AI frameworks including Caffe, TensorFlow, TensorFlow Lite, and a broad spectrum of neural networks including convolution and recurrent networks. This makes the DNA 100 processor an ideal candidate for on-device inferencing for vision, speech, radar, lidar and communication applications. The Tensilica Neural Network Compiler leverages a comprehensive set of optimized neural network library functions to map any neural network into executable and highly optimized high-performance code. As a result, the DNA 100 processor has robust software ecosystem support for different network types, including classification, object detection, segmentation, recurrent and regression. The DNA 100 processor also supports the Android Neural Network (ANN) API for on-device AI inference in Android-powered devices.

The DNA 100 processor can run all neural network layers, including convolution, fully connected, LSTM, LRN, and pooling. A single DNA 100 processor can easily scale from 0.5 to 12 effective TMACs, and multiple DNA 100 processors can be stacked to achieve 100s of TMACs for use in the most compute-intensive on-device neural network applications. The DNA 100 processor also incorporates a Tensilica DSP to accommodate any new neural network layer not currently supported by the hardware engines inside the DNA 100 processor, while also offering the extensibility and programmability of a Tensilica Xtensa core using Tensilica Instruction Extension (TIE) instructions. Because the DNA 100 processor has its own direct memory access (DMA), it can also run other control code without the need for a separate controller.

“Our customers’ neural network inference needs span a wide spectrum, both in the magnitude of AI processing and the types of neural networks, and they need one scalable architecture that’s just as effective in low-end IoT applications as it is in automotive applications demanding 10s or even 100s of TMACs,” said Lazaar Louis, senior director of product management and marketing for Tensilica IP at Cadence. “With the DNA 100 processor and our complete AI software platform and strong partner ecosystem, our customers can design products with the high performance and power efficiency required for on-device AI inferencing.”

The DNA 100 processor will be available to select customers in December 2018 with general availability expected in the first quarter of 2019.

About Cadence

Cadence enables electronic systems and semiconductor companies to create

the innovative end products that are transforming the way people live,

work and play. Cadence software, hardware and semiconductor IP are used

by customers to deliver products to market faster. The company’s System

Design Enablement strategy helps customers develop differentiated

products—from chips to boards to systems—in mobile, consumer, cloud

datacenter, automotive, aerospace, IoT, industrial and other market

segments. Cadence is listed as one of Fortune Magazine’s 100 Best

Companies to Work For. Learn more at

cadence.com .